## American University in Cairo

## **AUC Knowledge Fountain**

Theses and Dissertations

Student Research

6-1-2014

## Layout regularity metric as a fast indicator of process variations

Esraa AbdelAzim AbdelHamid Swillam

Follow this and additional works at: https://fount.aucegypt.edu/etds

#### **Recommended Citation**

## **APA Citation**

Swillam, E. (2014). *Layout regularity metric as a fast indicator of process variations* [Master's Thesis, the American University in Cairo]. AUC Knowledge Fountain.

https://fount.aucegypt.edu/etds/1243

#### MLA Citation

Swillam, Esraa AbdelAzim AbdelHamid. *Layout regularity metric as a fast indicator of process variations*. 2014. American University in Cairo, Master's Thesis. *AUC Knowledge Fountain*. https://fount.aucegypt.edu/etds/1243

This Master's Thesis is brought to you for free and open access by the Student Research at AUC Knowledge Fountain. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of AUC Knowledge Fountain. For more information, please contact thesisadmin@aucegypt.edu.

## The American University in Cairo

## School of Sciences and Engineering

# Layout Regularity Metric as a Fast Indicator of Process Variations

A Thesis Submitted to

Department of Electronics Engineering

In partial fulfillment of the requirements for the degree of Master of Science

by Esraa Swillam

under the supervision of Dr. Mohab Anis

March, 2014

## The American University in Cairo

School of Sciences and Engineering

## Layout Regularity Metric as a Fast Indicator of Process Variations

A Thesis Submitted by

Esraa AbdelAzim AbdelHamid Swillam

To the Department of Electronics Engineering

March/2014

In partial fulfillment of the requirements for The degree of **Master of Science**

Has been approved by

| Thesis Supervisor          |

|----------------------------|

| Affiliation:               |

| Thesis Internal Examiner   |

| Affiliation:               |

| Thesis Internal Examiner   |

| Affiliation:               |

| Department Chair/Director: |

| Date:                      |

| Dean:                      |

| Date:                      |

|                            |

## **Abstract**

Integrated circuits design faces increasing challenge as we scale down due to the increase of the effect of sensitivity to process variations. Systematic variations induced by different steps in the lithography process affect both parametric and functional yields of the designs. These variations are known, themselves, to be affected by layout topologies. Design for Manufacturability (DFM) aims at defining techniques that mitigate variations and improve yield. Layout regularity is one of the trending techniques suggested by DFM to mitigate process variations effect. There are several solutions to create regular designs, like restricted design rules and regular fabrics. These regular solutions raised the need for a regularity metric. Metrics in literature are insufficient for different reasons; either because they are qualitative or computationally intensive. Furthermore, there is no study relating either lithography or electrical variations to layout regularity. In this work, layout regularity is studied in details and a new geometrical-based layout regularity metric is derived. This metric is verified against lithographic simulations and shows good correlation. Calculation of the metric takes only few minutes on 1mm x 1mm design, which is considered fast compared to the time taken by simulations. This makes it a good candidate for pre-processing the layout data and selecting certain areas of interest for lithographic simulations for faster throughput. The layout regularity metric is also compared against a model that measures electrical variations due to systematic lithographic variations. The validity of using the regularity metric to flag circuits that have high variability using the developed electrical variations model is shown. The regularity metric results compared to the electrical variability model results show matching percentage that can reach 80%, which means that this metric can be used as a fast indicator of designs more susceptible to lithography and hence electrical variations.

## Acknowledgements

I would like to thank my supervisor, Dr. Mohab, for being helpful, flexible and supportive through the hard times I had during my graduate studies. I want to thank him for giving me the freedom to explore different research ideas and to choose what I loved. I, also, want to thank him, together with Dr. Ayman Elezabi in helping me in admission and guiding me to get a partial fellowship from the AUC which helped me a lot.

I wouldn't have been here without the love and support of my family, specially my mother and my husband who bore a lot with me and were always there to encourage and push me when I was down. My father and brother helped me a lot with their academic background. My sister and best friend love and support helped me through all the hard times.

I would like also to thank my company, Mentor Graphics for supporting part of the research and thank my manager, Omar Kamal, for his continuous encouragement and support. I want also to thank my technical leads, Andres Torres and Kareem Madkour and my colleague Sarah Mohamed for guiding me technically through different parts of this thesis.

Before all, I thank Allah for giving me the inspiration, power and persistence to do this work.

## **Contents**

| ΑI | bstrac            | ct                                |                                                       | ii |

|----|-------------------|-----------------------------------|-------------------------------------------------------|----|

| A  | cknov             | vledge                            | ments                                                 | i۱ |

| C  | onten             | ts                                |                                                       | ١  |

| Li | st of             | Figures                           | <b>3</b>                                              | vi |

| Li | st of             | Tables                            |                                                       | Ċ  |

| 1  | 1.1<br>1.2<br>1.3 | 1.1.1<br>1.1.2<br>1.1.3<br>Contri | tion                                                  | 3  |

| 2  | Bac               | karoun                            | d: Process Variations; Sources, Impact and Mitigation | 7  |

|    | 2.1               | _                                 | es of variation                                       | 8  |

|    |                   | 2.1.1                             | Photolithography                                      | ç  |

|    |                   | 2.1.2                             | Exposure                                              | 14 |

|    |                   | 2.1.3                             | Etch                                                  | 17 |

|    |                   | 2.1.4                             | Ion Implantation and Annealing                        |    |

|    |                   | 2.1.5                             | Chemical Mechanical Polishing (CMP)                   |    |

|    | 2.2               |                                   | t of Variations on Transistor Parameters              |    |

|    |                   | 2.2.1                             | Mobility $(\mu)$                                      |    |

|    |                   | 2.2.2                             | Oxide Capacitance $(C_{ox})$                          |    |

|    |                   | 2.2.3                             | Transistor Dimensions $(W, L)$                        |    |

|    |                   | 2.2.4                             | Threshold Voltage $(V_T)$                             |    |

|    | 2.3               |                                   | on Mitigation                                         |    |

|    |                   | 2.3.1                             | Architecture level                                    |    |

|    |                   | 2.3.2                             | Circuit level                                         |    |

|    |                   | 2.3.3                             | Device level                                          | 29 |

Table of Contents vi

| Bi | bliog           | raphy                                                                                                                                                       | 71                   |

|----|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| A  | Auto            | o-correlation based metric                                                                                                                                  | 67                   |

| 5  | 5.1             | Clusions And Future Work  Conclusions                                                                                                                       |                      |

|    |                 | 4.3.1 Publications Resulting From This Thesis                                                                                                               |                      |

|    | 4.3             | 4.2.3.1 Setup          4.2.3.2 Results          4.2.3.3 Discussion          Summary and Conclusion                                                          | 62<br>62<br>64       |

|    |                 | 4.2.1.1 Derivation of Regularity Metric 4.2.1.2 Variability Metric 4.2.1.3 Verification 4.2.2 Electrical Variability Modeling 4.2.3 Results and Discussion  | 55<br>58<br>60       |

| 4  | _               | Preliminary Exploration for Developing a Metric                                                                                                             | 52                   |

|    | 3.4             | 3.3.2 Fixed Origin Corner Square Inspection (FOCSI)                                                                                                         |                      |

|    | 3.3             | 3.2.1 Restricted Design Rules                                                                                                                               | 42<br>43             |

|    | 3.2             |                                                                                                                                                             | 38<br>39<br>40<br>40 |

| 3  | <b>Stat</b> 3.1 | e of the Art Layout Regularity Techniques  Effect of Layout Topologies  3.1.1 Delay  3.1.1.1 Poly Pitch and Orientation  3.1.1.2 Poly and Diffusion Density | 36<br>36<br>36       |

|    |                 |                                                                                                                                                             | 33                   |

|    |                 |                                                                                                                                                             |                      |

## **List of Figures**

| Process variation types and sources [1]                                                                                                                                                                                | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Illustration of the projection scanner exposure system. To print each lithographic field, the wafer and mask are translated in opposite directions in                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| a scanning fashion [2]                                                                                                                                                                                                 | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 21 · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                               | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                        | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                        | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                        | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

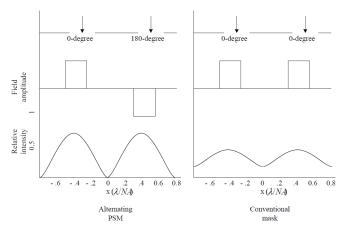

| Mask schematics and images of a line printed with alternating PSM and conventional mask [3]                                                                                                                            | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

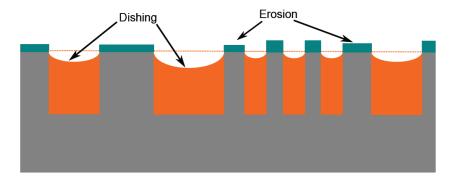

| Dishing of metal and erosion of inter-layer dielectrics in CMP. [4]                                                                                                                                                    | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

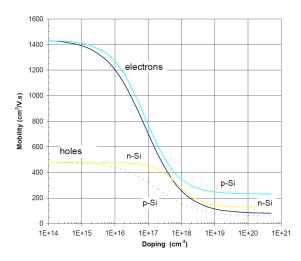

| Mobility as function of doping in Si [5]                                                                                                                                                                               | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

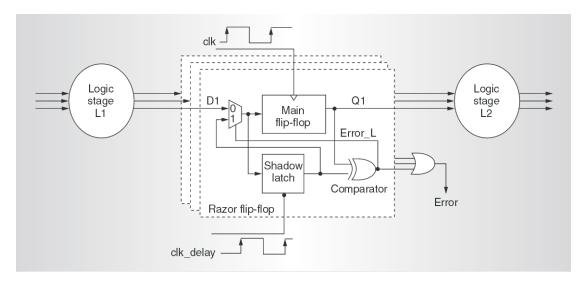

| Pipeline stage augmented with Razor latches and control lines[6]                                                                                                                                                       | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

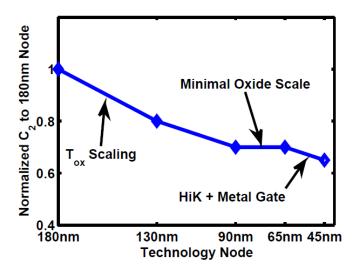

| Improvement in process due to oxide scaling and new materials [7]                                                                                                                                                      | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

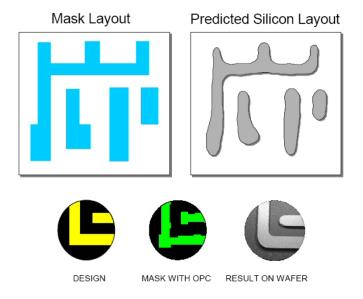

| Increasing geometrical primitives increases uncertainty in final design [8]                                                                                                                                            | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| ·                                                                                                                                                                                                                      | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

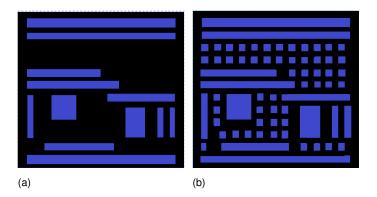

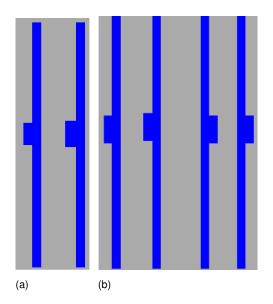

| Metal layer before and after dummy fill insertion                                                                                                                                                                      | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

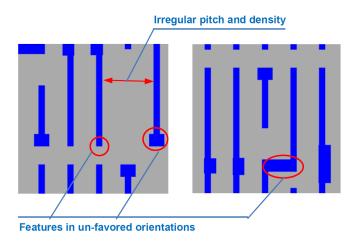

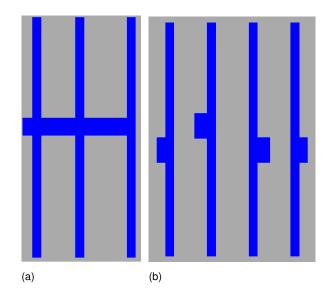

| Poly layouts of master slave flip-flop. a) Conventional layout. b) Litho-<br>driven layout, Poly lines restricted at contacted gate pitch. c) Layout b<br>with dummy Poly lines inserted at the missing CGP grid lines | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Post lithography aerial image of poly gate and diffusion showing NRG and line end shortening                                                                                                                           | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| L3GO Grid and Glyphs                                                                                                                                                                                                   | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

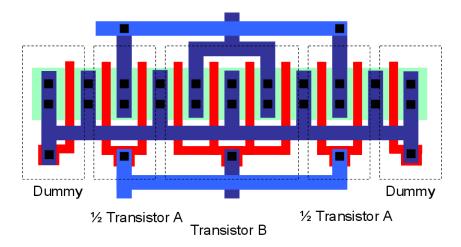

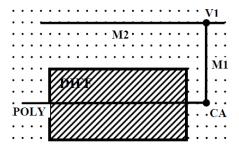

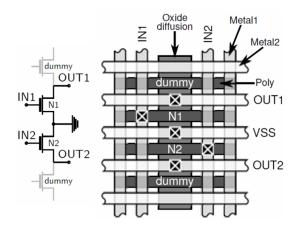

| VCTA schematic and layout for the NMOS transistor array with T=2                                                                                                                                                       | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

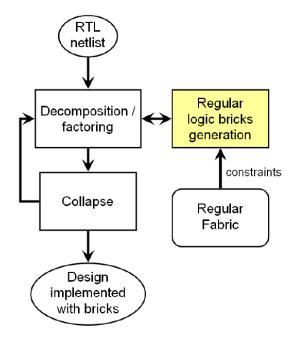

| Overall design flow for Regular Logic Bricks methodology                                                                                                                                                               | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                        | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| • • • • • • • • • • • • • • • • • • • •                                                                                                                                                                                | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

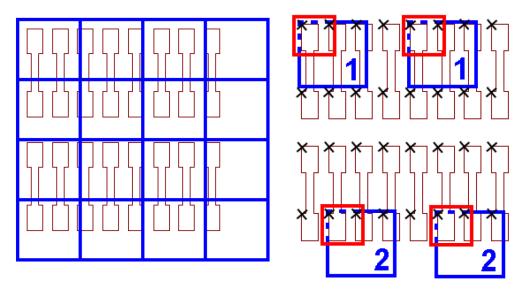

| the rigth)                                                                                                                                                                                                             | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Creating layout areas: contiguous squares (on the left) and FOCSI (on the rigth)                                                                                                                                       | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

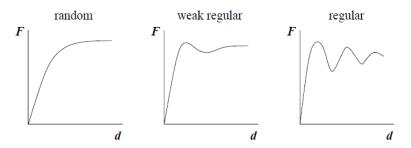

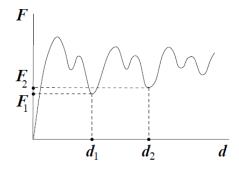

| Contrast curves of a random, a weak regular and a regular pattern [9]                                                                                                                                                  | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

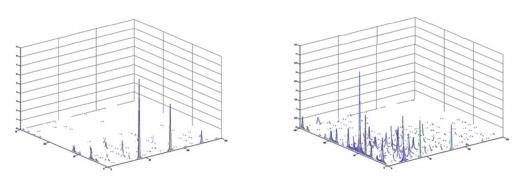

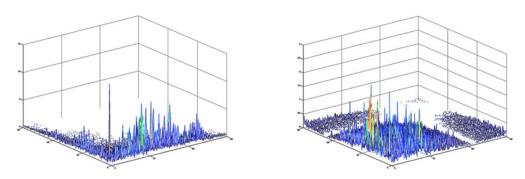

|                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                        | Illustration of the projection scanner exposure system. To print each lithographic field, the wafer and mask are translated in opposite directions in a scanning fashion [2].  Types of photoresists  Photoresist spin coating process  Photolithography and etching  Hammer head (on the left) and Serif (on the right)  Mask schematics and images of a line printed with alternating PSM and conventional mask [3]  Dishing of metal and erosion of inter-layer dielectrics in CMP. [4]  Mobility as function of doping in Si [5]  Pipeline stage augmented with Razor latches and control lines[6]  Improvement in process due to oxide scaling and new materials [7]  Increasing geometrical primitives increases uncertainty in final design [8]  Inter-digitized transistors with dummy transistor insertion at sides  Metal layer before and after dummy fill insertion  Poly layouts of master slave flip-flop. a) Conventional layout. b) Lithodriven layout, Poly lines restricted at contacted gate pitch. c) Layout b with dummy Poly lines inserted at the missing CGP grid lines.  Post lithography aerial image of poly gate and diffusion showing NRG and line end shortening  L3GO Grid and Glyphs  VCTA schematic and layout for the NMOS transistor array with T=2.  Overall design flow for Regular Logic Bricks methodology  SRAM Fourier transform of poly (on the left) and contacts (on the rigth)  Standard Cell Fourier transform of poly (on the left) and contacts (on the rigth)  Creating layout areas: contiguous squares (on the left) and FOCSI (on |

List of Figures viii

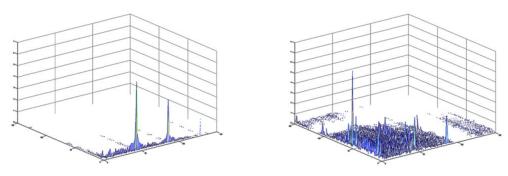

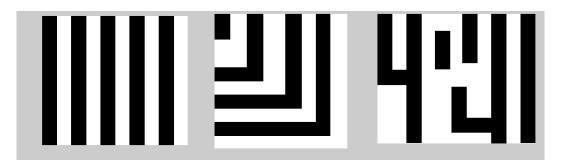

| 4.3  | Patterns 1, 2 and 3 respectively from left to right                  | 51 |

|------|----------------------------------------------------------------------|----|

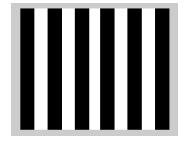

| 4.4  | Pattern 4                                                            | 51 |

| 4.5  | Most regular and least variable pattern                              | 53 |

| 4.6  | Two of the most irregular patterns for poly layer                    | 54 |

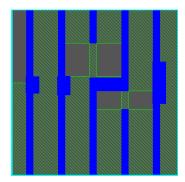

| 4.7  | Derived Layer in hashes(green)                                       | 55 |

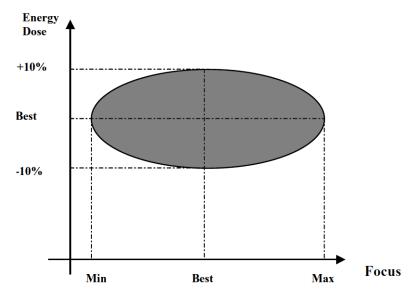

| 4.8  | Process Window                                                       | 56 |

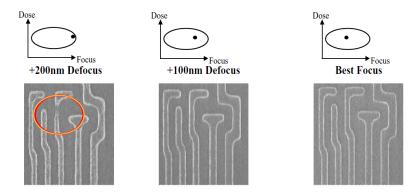

| 4.9  | Impact of process variations on printability                         | 56 |

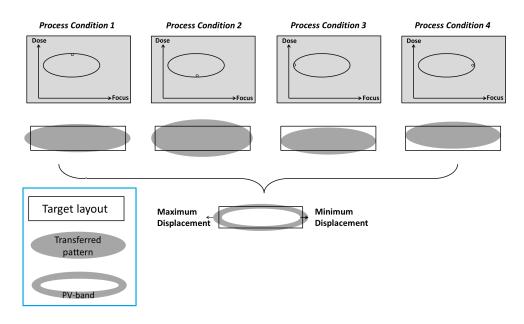

| 4.10 | PV-Band representing a set of simulated print images                 | 57 |

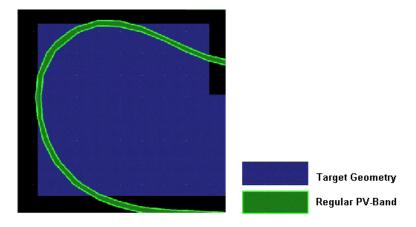

| 4.11 | Regular PVband                                                       | 57 |

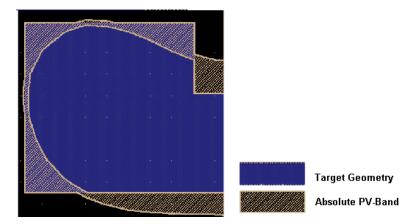

| 4.12 | Absolute PVband                                                      | 58 |

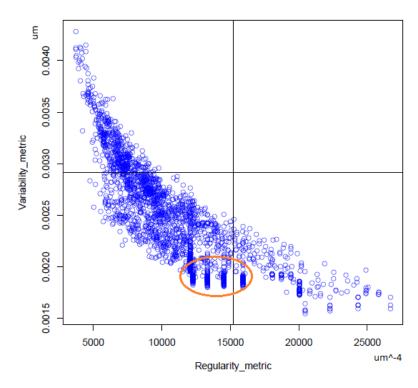

| 4.13 | Regularity metric versus process variability metric for each pattern | 59 |

| 4.14 | Pattern taken at the edge of two cells                               | 59 |

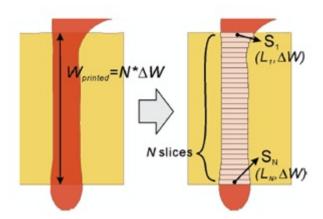

| 4.15 | The NRG device contour broken into parallel slices                   | 60 |

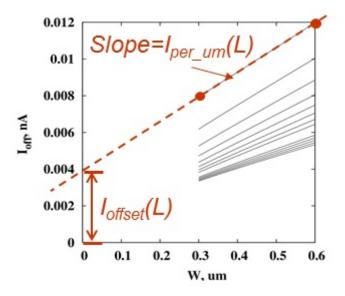

| 4.16 | Transistor current for different gates width (W) and length (L)      | 61 |

| 4.17 | Examples of misses                                                   | 63 |

| 4 18 | Examples of extras                                                   | 64 |

## **List of Tables**

| 2.1 | Process steps effect on transistor parameters[4]                          | 22   |

|-----|---------------------------------------------------------------------------|------|

| 4.1 | Regularity values for some patterns                                       | . 51 |

| 4.2 | Results of electrical variability and regularity of two different designs | 62   |

## **Chapter 1**

## Introduction

## 1.1 Motivation

Integrated Circuits design and manufacturing face increasing challenges as technology scales down to follow Moore's law. The main cause of these challenges is that the wavelength of light used in lithography (193nm) is much larger than the target features to be printed. Extreme Ultraviolet (EUV) was thought to be the enabler for 22nm and beyond, however its high cost and some technical challenges for volume production pushed the industry to find other solutions for getting smaller dimensions using the 193 nm light source [10].

This chapter gives a brief introduction about the efforts done to enable scaling in the form of resolution enhancement techniques. It will discuss one of the main challenges which is process variations, its sources and impact. Then, it will talk about the efforts in mitigating process variations and design for manufacturability techniques (DFM) as some of these efforts. The following part will discuss layout regularity and how designers headed towards more regular solutions to mitigate the effect of variations and how this raised the need for a regularity metric. Section 1.2 will show the contribution of this research and section 1.3 will brief how this thesis is structured.

## 1.1.1 Technology Scaling Down

The resolution limit of optical lithography is often discussed in the context of the famous Rayleigh criterion defined as

$$CD = k_1 \frac{\lambda}{NA} \tag{1.1}$$

where CD is the critical dimension,  $\lambda$  is the wavelength, and NA is the numerical aperture of optical system. The parameter  $k_1$  depends on the process specifications. Scaling down means smaller CD, to get smaller CD; NA should be increased,  $k_1$  and  $\lambda$  should be decreased. To increase NA a powerful system of lenses is being used together with the idea of immersion lithography. As can be noticed from (1.2), NA can be increased not only by increasing the size of the lens to increase  $\sin(\theta)$  but also by choosing a medium whose refractive index n is higher than that of air which is 1. This medium should have the following properties; low optical absorption at 193nm, compatible with photoresist and the lens material and non-contaminating. All these properties exist in pure water whose refractive index is 1.44.

$$NA = n\sin(\theta) \tag{1.2}$$

Another way to improve resolution for the same  $\lambda$  is through decreasing  $k_1$ , this is done by several resolution enhancement techniques (RET), examples of these are listed below:

- Optical Proximity Correction (OPC)

- Sub-Resolution Assist Features (SRAF)

- Phase Shifting Mask (PSM)

- Off Axis Illumination (OAI)

- Double Patterning

Each and every one of these techniques added more restrictions to design which made design rules very complex. Furthermore, abiding to design rules alone, still don't guarantee yield because of the non-linear effects induced by sub-wavelength fabrication and due to process variations which will be discussed in the following section.

#### 1.1.2 Process Variations

Variation is the deviation from intended or designed values for a structure or circuit parameter of concern. Process variations effect can be severe enough to affect the functional yield so that after printing the circuit doesn't work or it can affect the parametric yield so that the manufactured circuit works but with performance different from that of simulations. As minimum feature size decreases with scaling down, the effect of process variations becomes more and more dramatic as the tolerance becomes tighter.

There are two main categories for the sources of process variations; environmental and physical. This thesis concentrates more on the physical sources which arise mainly from different manufacturing steps as lithography, etching, ion implantation and chemical mechanical polishing.

## 1.1.3 Solutions for process variations

There are several techniques to mitigate the effect of process variations. Some are process-oriented and some are design oriented. Design oriented solutions includes design rules, layout modifications or robust circuit and system design. From the design oriented techniques to mitigate variations and improve yield comes the design for manufacturability branch of techniques.

Design for Manufacturing (DFM) are techniques that aim at improving the printability and yield through better communication between the design step and the manufacturing step [11]. DFM encourages ideas that provide better designs prior to manufacturing to decrease process variations effects and thus give better yield. DFM can be accomplished through a combination of minimizing process variations, and minimizing

device and circuit sensitivities to process variations. Many of the rules advocated in the DFM method include measures to mitigate pattern dependent variation, such as reduction of geometric primitives, layout regularity, redundancy techniques, pattern density uniformity, and optimal process feature sizing. Other areas of consideration in DFM are design for robustness and design for test[12]. This thesis concentrates on layout regularity as one of the trending techniques in mitigating process variations effect.

It was noticed that some designs and design styles are less sensitive to process variations, that's why SRAMs and FPGAs are the earliest products to migrate to a new, smaller, technology node. These design styles are able to reach high yield production level faster than other designs because they contain a very high degree of regularity. The repetitive bit-cells in SRAMs and Configurable Logic Blocks (CLBs) in FPGAs result in a limited number of unique geometry shapes in the layouts. One can afford to perform detailed analyses and simulations to employ strong-RETs on these shapes to improve manufacturability. The repetition of fundamental building blocks also enables the prequalification of the building blocks in silicon for known layout neighborhoods.

There are two types of regularity, the design regularity in which all building blocks have predictable neighborhoods is considered macro-regularity, and this is the type of regularity observed in SRAM and FPGAs. As feature sizes shrink, another type of regularity is indispensable which is micro-regularity. Micro-regularity is achieved by minimizing the number of unique geometry patterns used in a layout from a bottom-up approach by restricting the flexibility to draw arbitrary shapes. Constraints such as single width, single pitch, and single orientation of critical dimensions are imposed to enhance the printability and characterization predictability of critical layers. These constraints are imposed to enable and to simplify strong-RETs analyses and applications, thereby improving the printability of designs that adhere to micro-regularity [13]

## 1.2 Contribution

The contribution of this work is defining the required regularity for better robustness against process variations and coming out with a metric that can assess this regularity.

The main advantages of the regularity metric are that it is very fast; it takes a few minutes to run on a 1mm x 1mm design, it can be used to compare regularity of patterns within the same layout and it is closely correlated to the variations induced in lithography process so it can be used as a fast indicator of the patterns with high lithography variations.

This metric has the following possible usage scenarios:

- It can be used in pre-layout phase to help the designer create correct by construct patterns from the beginning.

- It may be used post layout in design verification phase to give something similar

to critical area analysis where it highlights the problematic patterns that are more

susceptible to process variations. The best practices deduced from the model

will be used to provide hints to the designer to help him solve these problematic

areas.

- Due to its simplicity and high speed, it can be used prior to lithographic simulations to select the areas of interest, which are areas that are more probable to have variations, then run lithographic simulations on only these areas to detect hotspots.

## 1.3 Structure of the thesis

This thesis is structured as follows; Chapter 2 gives the background needed to understand the basic manufacturing steps and their contribution as sources of variations, section 2.2 shows how variation impacts transistor parameters, while section 2.3 shows some variation mitigation methodologies on different design levels. Chapter 3 is dedicated to regularity, it starts with showing the effects of topology on electrical parameters in section 3.1 which clarifies the reason behind adopting regularity, then, in section 3.2, it shows the regular design solutions and how they evolved, section 3.3 shows the need for regularity metric and the existing metrics in literature. Chapter 4 shows the work done in deriving a regularity metric, it starts, in section 4.1, with a first trial using

image processing and Fourier transform then it shows the problems encountered in this methodology and how we moved to a geometry-based metric, then, in section 4.2, it shows the steps of deriving the geometry based metric and how it was validated against a variability metric that is a modified version of one found in literature, then it shows the work done to use the regularity metric as a fast indicator of electrical variability where it shows the comparison of regularity metric results to the results of a selected electrical variability method in literature.

## **Chapter 2**

# Background: Process Variations; Sources, Impact and Mitigation

Process variations are increasingly becoming the limiting factor in both IC design and manufacturing, so that, to a great extent, they dictated the style and progression of design in integrated circuits. Understanding the sources of process variations is critical to developing better design rules for circuits, ensuring accurate tests for robustness, and controlling manufacturing conditions for optimal design yield.

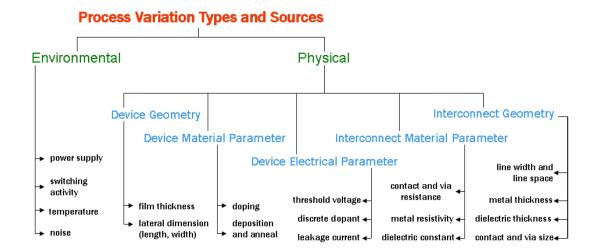

Process variations sources can be classified mainly into two categories *environ-mental* sources, those arise during the operation of a circuit, and include variations in power supply, switching activity, and temperature of the chip or across the chip. Variations resulting from environmental sources depend primarily on architectural and operating decisions such as power grid design and component placement. Time-varying variation in these environment parameters can be a significant design concern. The second category of variations, which is our main concern in this thesis, is due to *physical* factors. Examples of these physical factors are the fluctuations that appear during manufacturing and result in structural device and interconnect variations, which are essentially permanent. Physical variations can also be classified into device and interconnects and also into geometry, material, and electrical categories as shown in Figure 2.1.

FIGURE 2.1: Process variation types and sources [1]

As can be noticed from Figure 2.1, almost every step in the manufacturing process introduces variations in the end device which affect the functional and parametric yield of the whole design.

To understand more about physical process variations sources, this chapter provides a basic introduction to semiconductor processing. It gives a brief overview of some of the main manufacturing process steps and it places emphasis on variations introduced by each manufacturing step. The impact of variations on different transistor parameters is discussed in section 2.2.

Because the manufacturing process may never be deterministic, designers always try to use design techniques and methodologies that are known to reduce process variation. Accordingly, the last section shows the different approaches followed to mitigate variation effects in each design level.

#### 2.1 Sources of variation

There are several steps in integrated circuits fabrication. Theses steps can be classified into front-end processes and back-end processes. The front-end ones are those related to fabrication of devices like MOS transistors. They involve oxidation, doping and annealing with some patterning and etching steps. On the other hand, back-end

processes are those involved in creating interconnect wires, they include metallization, deposition and chemical mechanical polishing [14].

Some of these process steps are considered to be major sources of variation, these are: 1) photolithography, 2) etching, 3) ion implantation and rapid thermal annealing, and 4) chemical-mechanical polishing (CMP). The effect of variations of each step depends on the feature being fabricated, so that each process step affects subsequent transistor and interconnect parameters. For example, variations in lithography and etch affect the physical dimensions of transistors. CMP variations affect wires and vias that form the interconnect between transistors. On the other hand, variations in ion implantation and rapid thermal annealing directly impact the doping of transistors. One more thing to be considered is that the the impact of variations in a certain process step also depends on the application in which the fabricated transistor is used. For example, variation in the size of the source/drain area of a transistor has much greater impact on the overall performance when that transistor is used in an analog versus digital application [4]. The following sections will show in details some of the process steps and how they contribute as sources of variations.

## 2.1.1 Photolithography

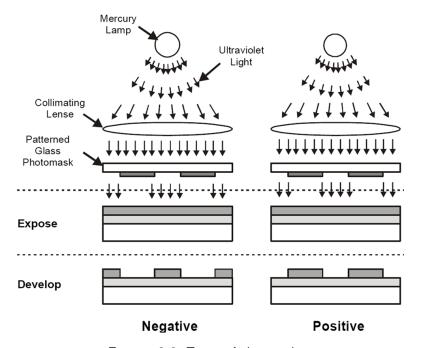

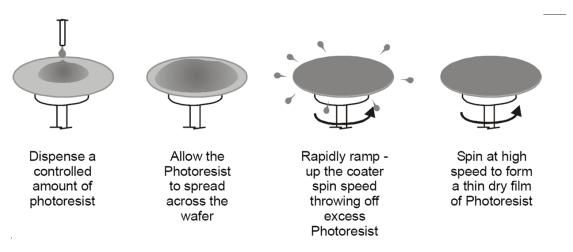

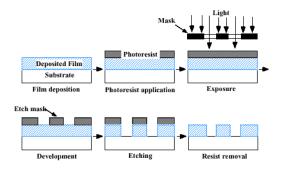

Photolithography is the first step in IC manufacturing. It consists of several steps that start with photoresist application followed by exposure, baking and development. Photolithography is also one of the main contributors to physical variations. The subsections below are going to discuss the different steps in photolithography, the challenges each one has and also the variations they introduce.

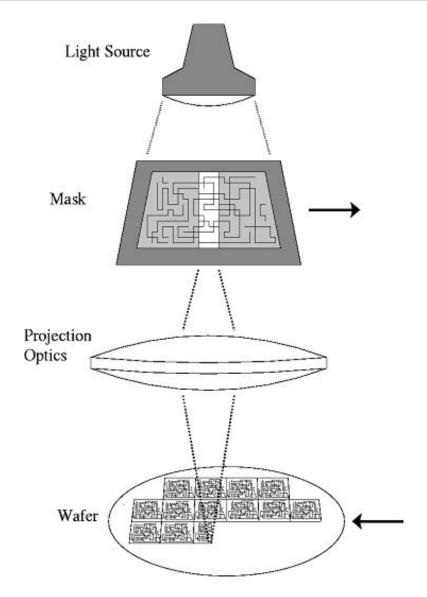

The current industry method is projection printing. The exposure system consists of three main components. First, a source of light at a particular wavelength is needed (193 nm). Second, a reticle or mask that has the desired pattern drawn in the form of transparent and opaque areas. The light is passed through the mask to transfer that pattern onto the photoresist-coated wafer. The pattern on the mask is greater than the desired one on the wafer so the mask pattern is demagnified as it is transferred to the

wafer. To accomplish this image reduction, the third component of the exposure system, a lens consisting of several optical elements (called projection optics), is required to project a reduced image of the mask onto the target wafer. The mask is exposed to light together with the wafer that has been coated by photoresist.